숭실대학교 하석재 교수님의 2022-1학기 컴퓨터 구조 강의를 정리 및 재구성했다.

- 추상화란?

- 하드웨어와 소프트웨어의 생산성을 높이기 위한 핵심 기술 중 여러 수준에서 설계를 명시하는 것으로, 하위 수준에서 상세한 사항을 안 보이게 함으로써 상위 수준 모델을 단순화 시키는 방법이다.

-ISA(Instruction Set Architecture)

-하드웨어와 최하위 계층 소프트에어 사이의 인터페이스

-마이크로프로세서가 인식해서 기능을 이해하고 실행할 수 있는 기계어 명령어

-마이크로프로세서마다 기계어 코드의 길이와 숫자 코드가 다르다.

-기계어/어셈블리 프로그램을 작성하기 위해서 알아야하는 모든 정보를 말한다.

-레지스터, 메모리 접근, 입출력 등

-프로그래머가 저수준 세부사항까지 걱정할 필요는 없다.

-ABI(Application Binary Interface)

- 응용프로그래머에게 제공되는 기본 명령어 집합과 운영체제 인터페이스를 합친 것

Ex)

- Windows(X86)vs Windows RT (ARM)

-Android(ARM) vs X86 안드로이드(X86)

- 인터페이스는 비슷해보이지만 어느 프로세서에서 작동하는 지가 다르다.

- 최종 바이너리 프로그램을 그대로 쓸 수 없고 동일한 소스코드를 실행하려면 타겟을 지정해서 새로 컴파일 해줘야한다.

-vs API (Application Programming Interface)

-메모리의 종류

- Ram vs Rom

- Ram: 읽기, 쓰기가 가능하 여러 번 쓸 수 있다. Rom보다 빠르다

- Rom : 읽기만 가능하다.

-Erasable Rom

-삭제가능한 Rom

-ex) EPROM, EEPROM

-Flash Memory

-EEPROM의 변형 / 속도가 개선됨

[종류]

-NAND (최근 주류, 저렴하고 속도가 느리다. 삼성/ Sk 하이닉스)

-NOR (고가이며, 속도가 빠르다. 마이크로 / 인텔)

- 3D 적층 기술

- 셀을 높게 쌓은 단수에 따라 기술의 수준이 나뉜다.

-현재 96층 3D NAND 에서 192층으로 발전중

-일반 반도체는 적층형을 연구하고 있다.

-소자 하나에 여러 개의 비트를 기록가능하다

-Ex) SLC(1), MLC(2), TLC(3) ...

-기본적으로 쓰기 수명이 존재한다.

- 소자의 수명과 속도를 개선하기 위해서 연구를 진행하는 중이다.

-wear leveling : 셀을 골고루 돌아가면서 읽기/쓰기를 할 수 있도록 하는 기능이다. 지속적으로 읽기/ 쓰기

반복되면 수명이 떨어져 결국 데이터를 저장 할 수 없는 데드셀이 생기게 되는데, 이를 막아 수명을 유지하는 기술이다. (깎이는 셀만 깎이지 않게)

- 개인 휴대용 기기는 크기와 모양의 제약으로 인해 자기디스크 대신 사용한다.

-Volatile vs Non-Volatile

-Volatile : Ram

-Nom-Volatile : Rom , Flash memory

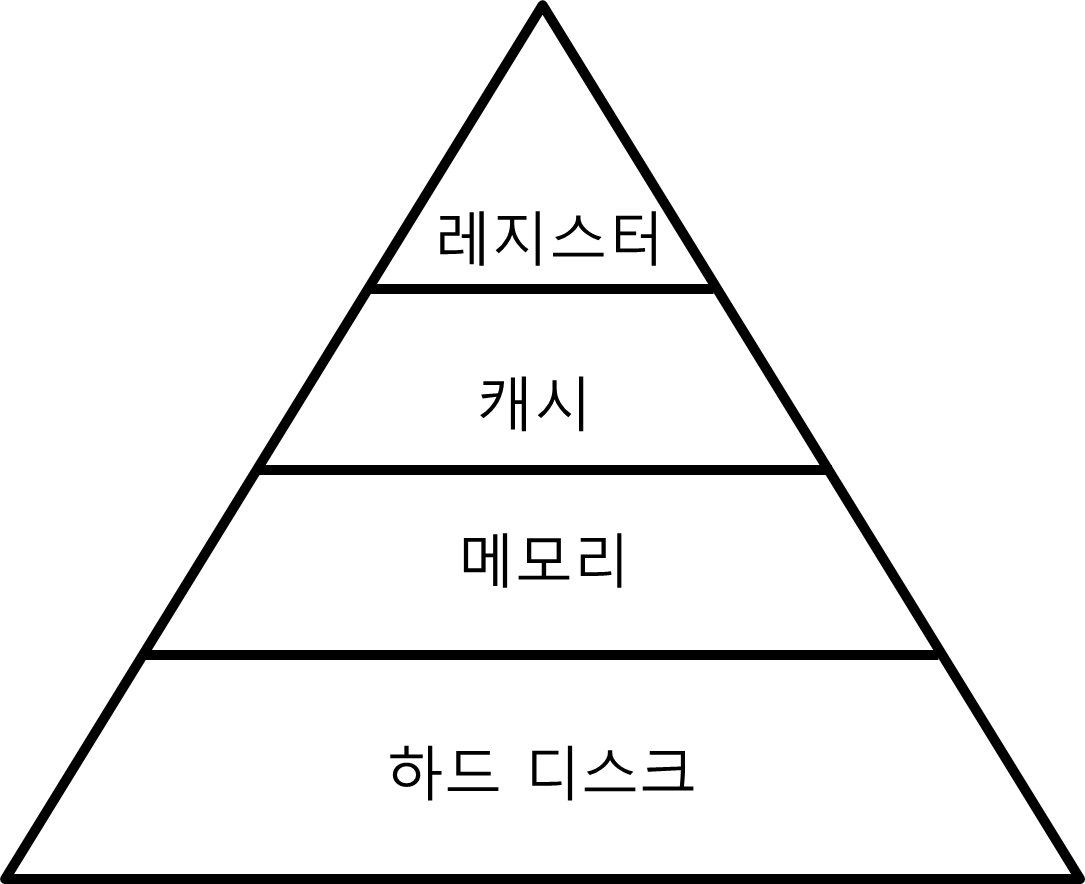

-메모리 계층 구조란?

- 메모리를 필요에 따라 여러가지 종류로 나누어 둠을 의미한다.

-이 때 필요한 대부분의 경우라 CPU가 메모리에 더 빨리 접근하기 위함이다.

-속도가 빠른 캐시메모리와 속도가 느린 일반 메모리로 구분된다

-이 때, 캐시메모리는 주로 SRAM, 일반 메모리는 DRAM이 쓰인다.

-SRAM vs DRAM

-SRAM은 Fip-flop을 기본 소자로 한 조합논리 (combinational logic)이다.

-DRAM은 RLC중 capacitor 기반으로 리프레시가 필요하다.

- 빠른 메모리와 느린 메모리 사이의 블렌딩(blending)을 통해, 속도는 빠른 메모리에, 용량/가격은 느린 메모리

에 가깝게 만들려는 시도가 이루어진다.

-반도체 (트랜지스터)

- 반도체 : 어떤 때는 전기가 통하거(도체) 어떤 때는 전기가 통하지 않는 물질(부도체)이다.

- 트랜지스터 : 전기 신호로 제어되는 on/off 스위치이다.

- 초기에는 백열 전구로 구현했으나 전력 및 발열을 줄이면서 현재는 주로 실리콘 소재로 만든다. (Cmos = Mmos + Pmos)

-무어의 법칙

- 인텔 창업자 고든 무어가 주장했다고 알려지며, 반도체의 트랜지스터 집적도의 증가도에 대한 법 칙

- 반도체 칩에 집적할 수 있는 트랜지스터의 숫자가 적어도 매 18개월마다 두 배씩 증가한다는 내용이다.

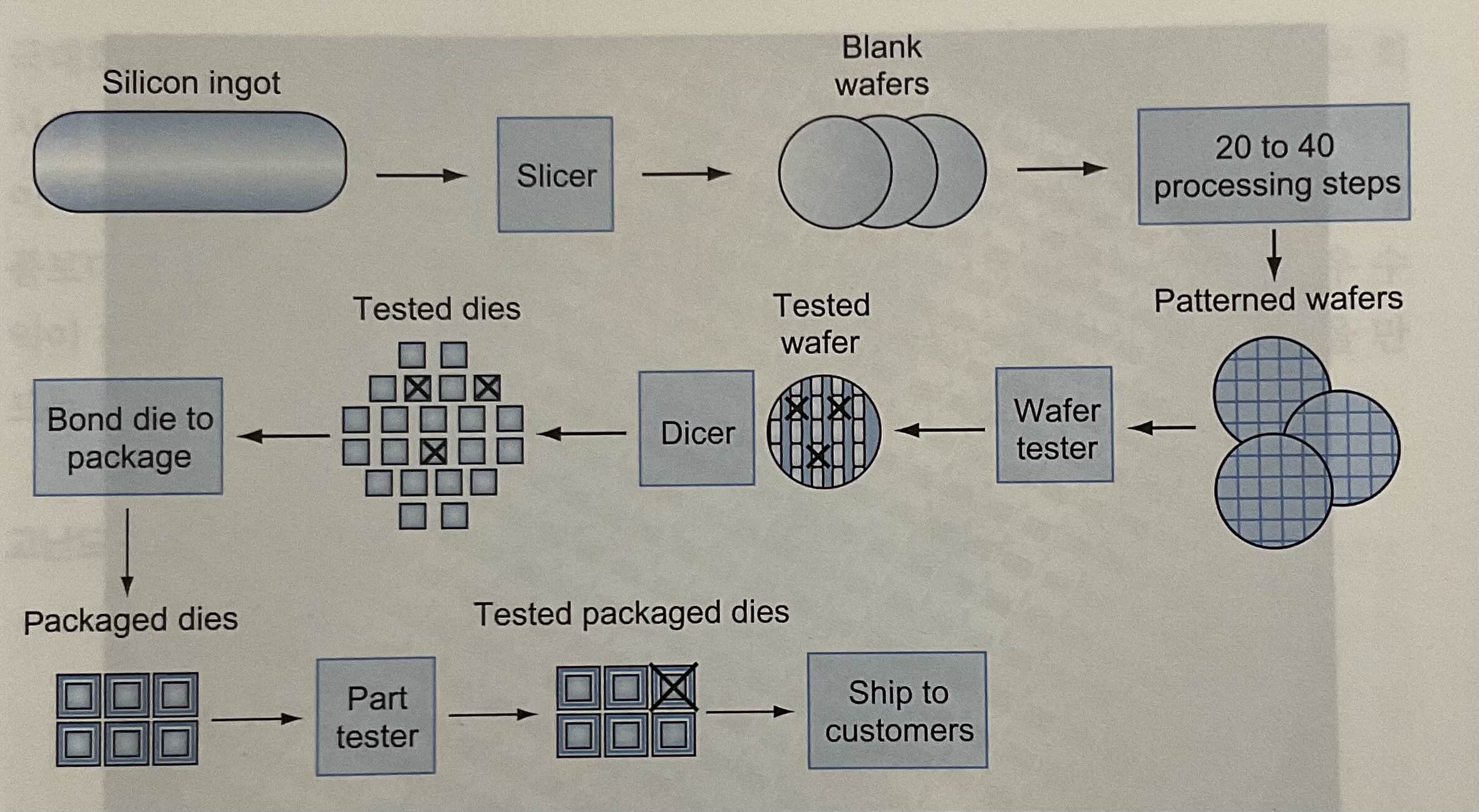

-칩 생산 공정

-과정

- 실리콘 결정괴(silicon crystal)를 자른 후 실리콘 웨이퍼(wafer)를 만든다.

- 빈 웨이퍼에 패턴을 새긴다. (patterned wafers, 노광 작업)

- 패턴이 새겨진 웨이퍼를 웨이퍼 검사기로 검사해서 불량 부분에 표시를 한다. (tested wafer)

- 다이(tested dies)가 만들어지고, 검사에 통과한 다이들의 개수를 통해 양품률(yield)를 계산한다.

- 검사에 통과한 다이는 패키지에 붙이고 (bond die to package) 납품하기 전 다시 한 번 검사를 거친다.

- 일반적인 반도체 개발 사이클

- 설계 -> 양산 성공 -> 수율 개선

- 나노미터 공정

- 반도체 안에서의 전기회로의 선폭(전기가 지나다니는 길)을 작게 하려는 노력들이 이어지고 있다.

[장점]

-공정이 미세할수록 다이(die) 크기를 줄일 수 있고, 한 웨이퍼로 더 많은 집적회로를 생산할 수 있다.

- 같은 다이안에 더 세밀하게 회로를 새길 수 있으니 트랜지스터도 더 많이 넣을 수 있다.

[예시]

- 현재 2022 기준

-5nm 적용(애플 M1, A15)

-7-8nm 적용 (AMD Ryzen/ Nvidis 30 series GPU)

- 실리콘 웨이퍼 생산

- 웨이퍼에 노광용 레이저를 이용해 패터닝 작업을 진행한다.

-사진 인화와 유사한 과정

- 리소그래피 (Lithography)

- ASML이 관련 대표회사.

'컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 프로세서 (0) | 2022.08.28 |

|---|---|

| [컴퓨터 구조] 컴퓨터 연산 (0) | 2022.08.26 |

| [컴퓨터 구조] 명령어 종류, 기능과 형식 (0) | 2022.08.24 |

| [컴퓨터 구조] 성능 평가 (0) | 2022.08.23 |

| [컴퓨터 구조] 컴퓨터 구조 기초 (0) | 2022.08.21 |