[컴퓨터 구조] 단일 사이클 구현 (2)

숭실대학교 하석재 교수님의 2022-1학기 컴퓨터 구조 강의를 정리 및 재구성했다.

*이 절에서 설명한 단일 사이클 패스는 명령어 메모리와 데이터 메모리를 따로따로 가져야 한다.

1. MIPS에서는 데이터와 명령어의 형식이 달라서 다른 메모리가 필요하기 때문

2. 메모리를 별도로 갖는 것이 저렴하기 때문 (듀얼 포트와 비교했을 때)

3. 프로세서가 명령어를 한 사이클에 실행하는데, 단일 포트의 메모리로는 한 사이클에 2개의 서로 다른 접근을 할 수 없기 때문

[단순 구현 데이터 패스]

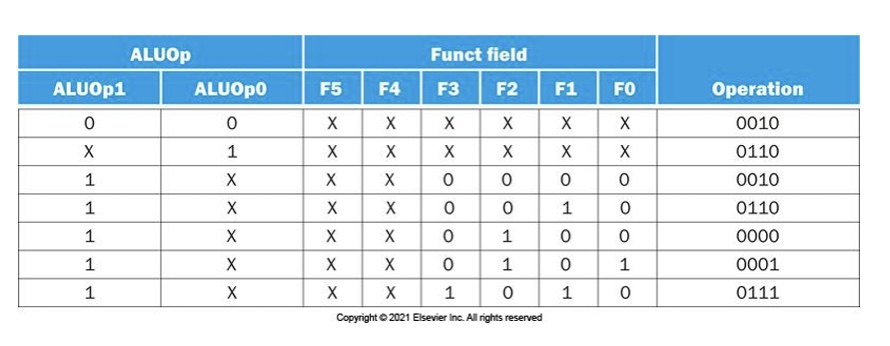

[ALU 연산]

: ALU는 명령어 종류에 따라 첫 다섯 가지 기증 중 하나를 수행하게 된다.

-Load/ Store 명령어인 경우에는 메모리 주소를 계산하기 위한 add 연산을 하는 데 ALU를 사용한다.

- Branch는 같은 지 비교를 위해 subtract 연산을 수행한다.

-R형식 명령어의 경우에는 명령어 하위 6비트의 funct 필드 값에 따라서 다섯 가지 연산 (And, Or, subtract, add set on less than) 중 하나를 수행하게 된다.

: ALU 제어 비트들은 ALUOp 제어 비트와 R형식 명령어의 funct필드 값에 의해 저장된다.

-첫 번째 나열된 opcode가 ALUOp 비트 값을 결정한다.

-ALUOp 값이 00이나 01일 때, ALU 동작은 funct 필드에 영향을 받지 않는다. (don't care , xxxxxx으로 표시)

- ALUOp가 10일 때는, funct 필드 값이 ALU 제어 입력을 결정하는 데 쓰인다.

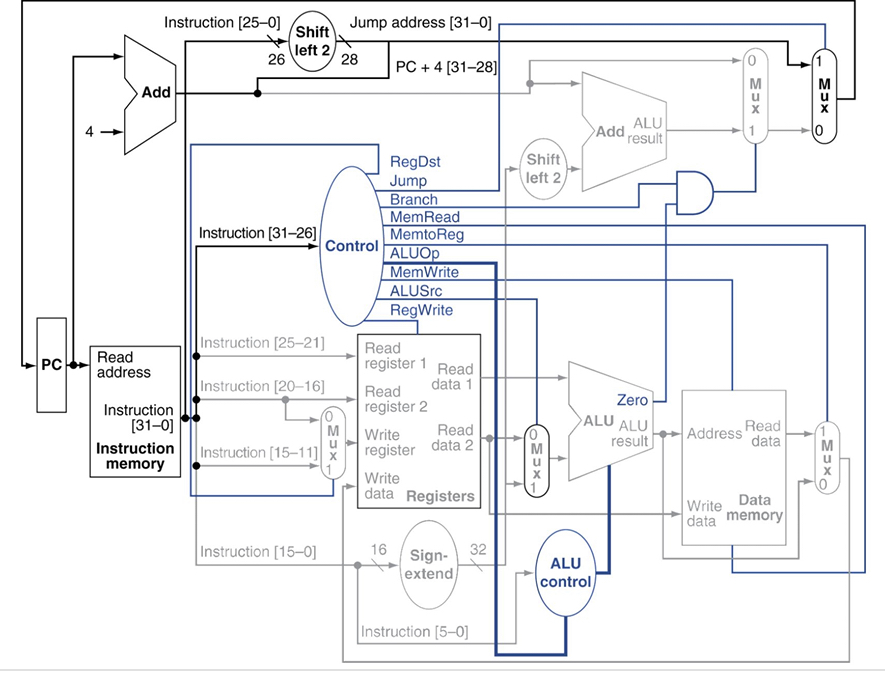

[주제어 유닛의 설계]

-opcode라 불리는 op 필드는 항상 비트 31:26에 들어있다. (Op[5:0])

-읽을 레지스터 2개는 항상 rs, rt 필드에 의해 지정되는데, rs, rt 필드는 비트 25:21과 비트 20:16에 있다. R형식 명령어와 같을 시 분기 및 저장 명령어에 저장된다.

-적제 명령어와 저장 명령어를 위한 베이스 레지스터는 항상 비트 25:21(rs)에 있다.

-같을 시 분기, 적재, 저장 명령어를 위한 16비트 변위는 항상 비트 15:0에 있다.

- 제어 유닛의 입력은 명령어의 6비트 opcode 필드이다.

- 제어 유닛의 출력은

멀티플렉서를 제어하는 데 쓰이는 3개의 1비트 신호 (RegDst, ALUsrc, MemotoReg),

레지스터 파일과 데이터 메모리에서 읽고 쓰는 것을 제어하기 위한 3개의 신호(RegWrite, MemRead, MemWrite),

분기할지 말지를 판단하는데 쓰이는 1비트 신호(Branch)

ALU를 위한 2비트 제어신호(ALUOp)이다.

-분기 제어 신호와 ALU의 Zero출력을 결합하는데 AND 게이트를 사용한다. 이 AND 게이트 출력은 다음 PC값을 선택하는 데 쓰인다.

-PCSrc는 제어 유닛으로부터 직접 나오는 값이 아니고 만들어야 되는 신호이다.

- 입력이 2개인 멀티플렉서의 1비트 제어 신호가 인가되면 멀티플렉서는 1번 입력을 선택한다. 제어가 인가되지 않으면 멀티플렉서는 0번 입력을 선택한다.

: 제어 신호들의 값은 명령어의 opcode 필드에 의해서만 결정된다.

[R형식 명령어]

-명령어 모두의 근원지 레지스터 필드는 rs, rt이고 목적지 필드는 rd이다. 이 사실에서 ALUSrc와 RegDst 값이 결정된다.

- 레지스터에 쓰기를 하지만(RegWrite=1), 데이터 메모리를 읽거나 쓰지는 않는다.

- Branch 제어 신호가 0 일때, PC는 무조건 PC+4로 바뀐다. (Branch가 1이고 ALU Zero 출력이 1이면 PC에 분기 목적지 주소가 들어간다.)

- ALUop는 func필드를 보고 ALU 제어 신호를 만들어야하므로, ALUOp필드가 10이 된다.

[lw/ sw]

-ALUSrc와 ALUOp 값은 주소 계산에 적합하게 정해진다.

-MemRead와 MemWrite는 메모리 접근을 할 수 있도록 설정된다.

-RegDst와 RegWrite는 적재 명령어가 결과를 rt 레지스터에 저장할 수 있게 정해진다.

[beq]

: rs와 rt 레지스터 값을 ALU에 보내기 때문에, R형식 연산과 비슷하다.

-ALUOp 필드는 같은지 비교하기 위한 뺄셈을 하도록 설정된다(ALU 제어=01)

-RegWrite 신호가 0이므로, MemtoReg 값이 무엇이 되든 상관이 없다.

-레지스터에 쓰지 않으므로 Write때는 RegDst도 don't care가 된다.

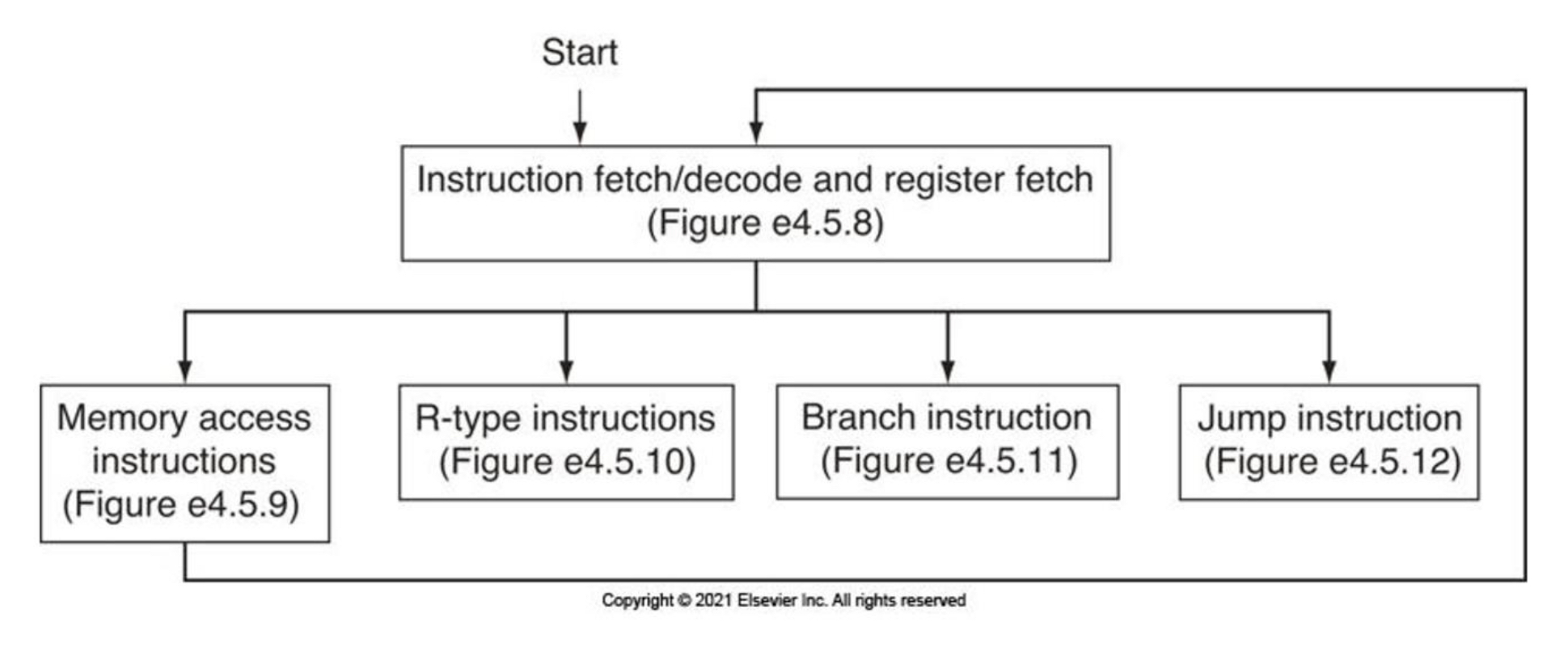

[데이터 패스의 동작]

[R-type Instruction (add $t1, $t2, $t3)]

순서

1. 명령어를 인출하고 PC를 증가시킨다.

2. 레지스터 파일에서 두 레지스터 $t2와 $t3를 읽는다. 동시에 주 제어 유닛은 제어선 값들을 결정한다.

3. ALU는 레지스터 파일에서 읽어들인 값들에 대해 연산을 하는데, 기능 코드 (명령어의 funct 필드인 비트 5:0)를 사용하여 ALU 제어 신호를 만든다.

4. ALU의 결과 값을 레지스터 파일에 쓰되 명령어의 비트 15:11을 이용하여 목적지 레지스터($t1)을 선택한다.

[Load Instruction (lw $t1, offset($t2))]

순서

1. 명령어를 명령어 메모리에서 인출하고 PC 값을 증가시킨다.

2. 레지스터 파일에서 레지스터 $t2를 읽는다.

3. ALU는 레지스터 파일에서 읽어 들인 값과 명령어의 하위 16비트(offset)를 부호확장한 값의 합을 구한다.

4. 이 합을 데이터 메모리 접근을 위한 주소로 사용한다.

-저장 명령어와의 비교

: 저장 명령어도 비슷하게 동작하는데, 큰 차이점은 메모리 제어가 읽기가 아닌 쓰기이며, 읽어 들인 두 번째 레지스터 값이 메모리에 저장할 데이터가 되고, 데이터 메모리 값을 레지스터 파일에 쓰는 동작은 일어나지 않는다는 점이다.

[Branch on equal Instruction( beq $t1, $t2, offset)

: 같을 시 분기 명령어의 동작이다

순서

1. 명령어를 명령어 메모리에서 인출하고 PC값을 증가시킨다.

2. 레지스터 파일에서 두 레지스터 $t1과 $t2를 증가시킨다.

3. ALU는 레지스터 파일에서 읽어 들인 값들에 대해 뺄셈을 한다. 명령어의 하위 16비트 (offset)를 부호확장한 후 2비트 왼쪽 자리이동한 값에다 PC+4 값을 더한다. 이 값이 분기 목적지 주소이다.

4. 어떤 덧셈기의 결과를 PC에 저장할지 ALU의 Zero 출력을 이용하여 결정한다.

[Jump 명령어 추가]

-Jump는 word 주소 기반

-PC를 이전 PC의 4비트 + 26비트 jump 주소 + 00과 같은 형식으로 세팅 (총 32비트)

-Opcode에서 추가 제어 신호(control signal)이 필요함.

[단일 사이클 구현의 문제]

- 비록 단일 사이클 설계가 올바르게 작동한다 하더라도 비효율성 때문에 현대적 설계에서는 쓰이지 않는다. 그 이유는 단일 사이클 설계에서는 클럭 사이클이 모든 명령어에 대해 같은 길이를 가져야 하기 때문이다.

- 물론, 클럭 사이클은 컴퓨터에서 가능한 경로 중 가장 긴 경로에 의해 결정된다. 이 최장 경로(Critical Path)는 적재 명령어이고, 클럭 사이클을 적재 명령어에 맞춰야 한다.

- CPI 값은 1이지만 단일 사이클 구현은 클럭 사이클이 너무 길기 때문에 전체 성능이 좋지 않다.

- 앞에서 다뤘던 매우 간단한 명령어 집합을 가졌던 초창기의 컴퓨터는 이러한 구현 방법을 사용하였지만, 부동 소수점 유닛을 구현하려 하거나 좀 더 복잡한 명령어를 갖는 명령어 집합인 경우에는 단일 사이클 구현은 잘 작동하지 않을 것이다.

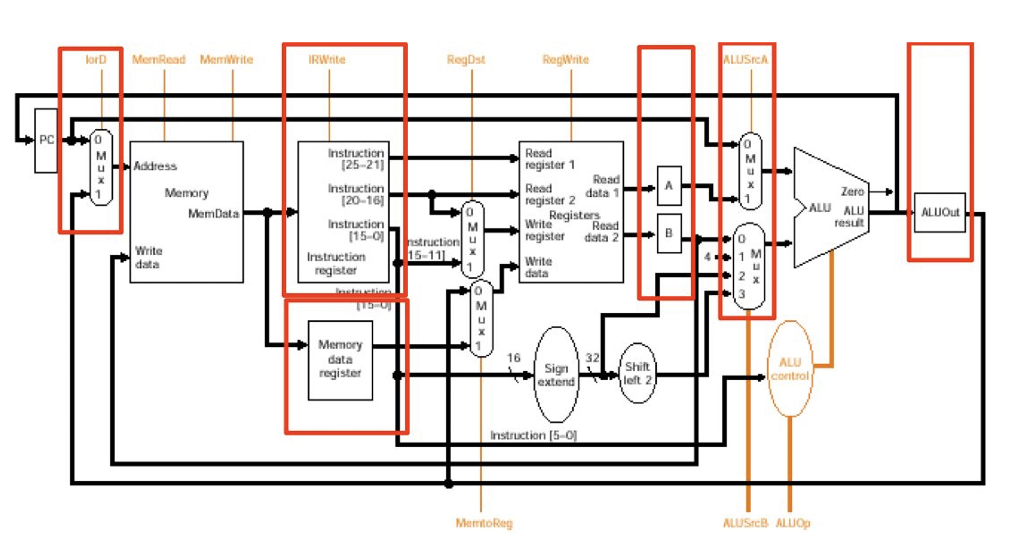

[멀티 사이클 구현]

: 멀티 사이클 구현에서는 명령어 실행의 각 단계가 한 클럭 사이클씩 걸린다.

- 명령어마다 필요한 클럭 수가 달라질 수 있다.

- 한 명령어 안에서 기능 유닛 여러 번을 사용 가능하다.

- 한 명령어 실행 안에서 기능 유닛을 공유 가능하다. 이러한 공유는 필요한 하드웨어의 양을 줄일 수 있게 해준다.

- 추가 Mux, 임시 레지스터, 제어신호등이 필요하다.